Mein letztes Projekt begann mit dem Grundverfahren über eine Kapazitätsmessung die Feuchtigkeit von Erde zu messen.

Soweit dürfte das manchen bekannt sein. Angefangen hat es mit der Idee ein vollautomatisches Bewässerungssystem für Topfpflanzen zu bauen.

Also ein Arduino Micro als MCU bestellt und los ging es.

Erste Messungen ergaben eine Änderung bei Feuchtigkeitsänderung. OK machbar.

Gerät und Elektronik gebaut, Pumpe usw funktioniert soweit. UND DANN

hat es einfach nicht so funktioniert wie es sollte.

Ok genauer messen, Messdaten in Logfile schreiben Langzeitmessung mit Vergleichsmessung

Erweiterung der Messanordnung auf einen STM32 mit mehreren Kanälen, 3x4 Tastatur und LCD 20x4 Anzeige.

Hier habe ich festgestellt, dass meine Messwerte zum einen massive Schwankungen haben und zum anderen ständig sinken. Letzteres kann eigentlich nicht wirklich sein, denn eine feste Kapazität dürfte das ja nicht außer ???

Ja Temperatur und Abgeschirmt ist es auch nicht ... das C Program auf dem Mikrocontroller über die Interuptrutine und sequenzielle Abarbeitung ... naja ok dem kann man ausweichen

Neue Messanordnung mit CPLD und Schmitt Triger Schwingkreis

Der CPLD übernimmt die gesamte Zeitkritische Messung und gibt an die MCU per SPI die Daten weiter, welche diese in ein Logfile schreibt.

Kurz um, es bedurfte hierfür eines RS FlipFlops, kennt jeder Elektroniker.

Man erwartet natürlich dass in Alteras Quartus sowas drin ist

ist es auch allerdings mit Takt (CLK)

Google ergab XXX Treffer auf RSFF

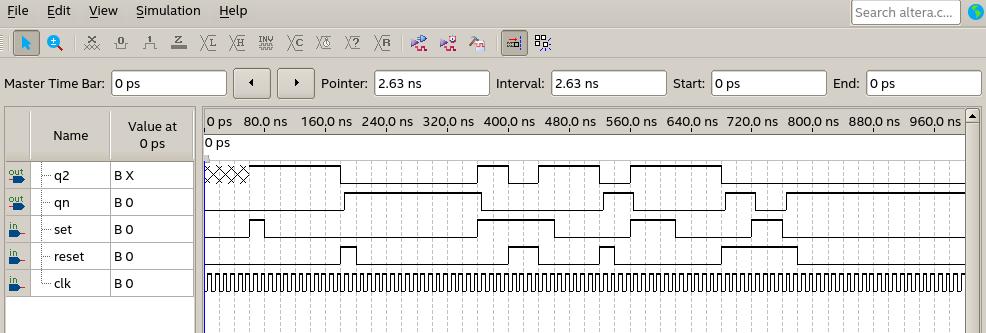

nun testete ich diverse VHDL Code Beispiele auf dem Quartus ModelSim Simulator

Dabei fand ich schon lustig, dass von einer Hochschule ein VHDL Code veröffentlicht war, welcher nicht funktionierte.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity RSFF is

port (R, S : in bit;

Q, Q_n : out bit);

end RSFF;architecture V1 of RSFF is

signal nand1, nand2: bit;begin

nand1 <= NOT (S AND nand2);

nand2 <= NOT (R AND nand1);

Q <= nand1;

Q_n <= nand2;

end V1;

schaut doch auf den ersten Blick gut aus ! ?

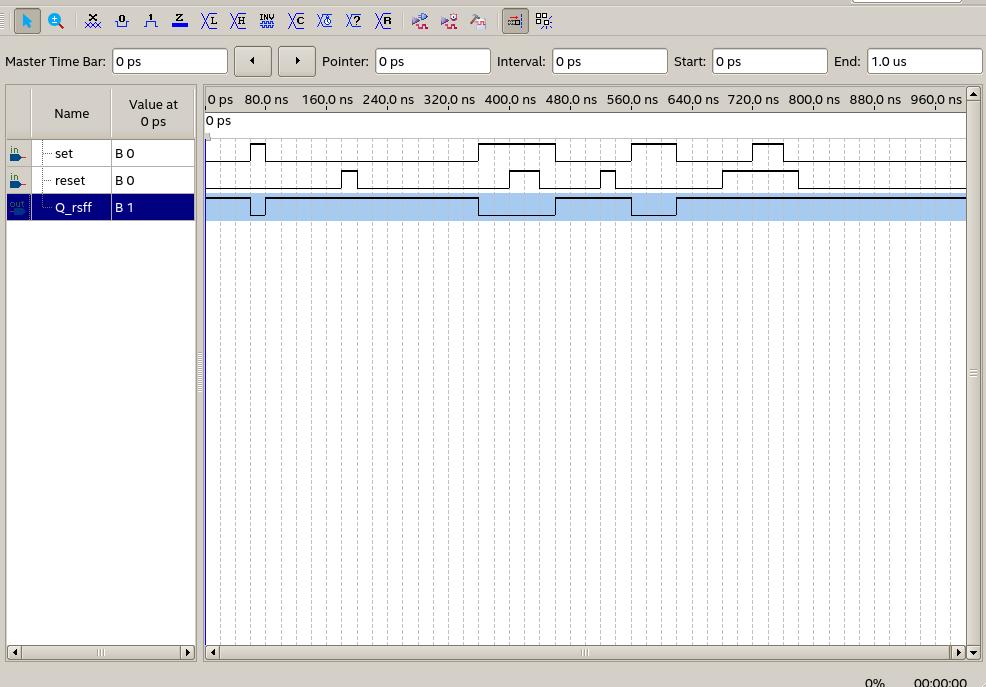

Aber die Simulation zeigt eindeutig, dass der Reset nicht funktioniert !!

Die Version von Quartus toggelt mit dem Takt wenn R&S High sind OK

ohne Takt gehts nicht .

Error (275044): Port "CLK" of type SRFF of instance "inst5" is missing source signal

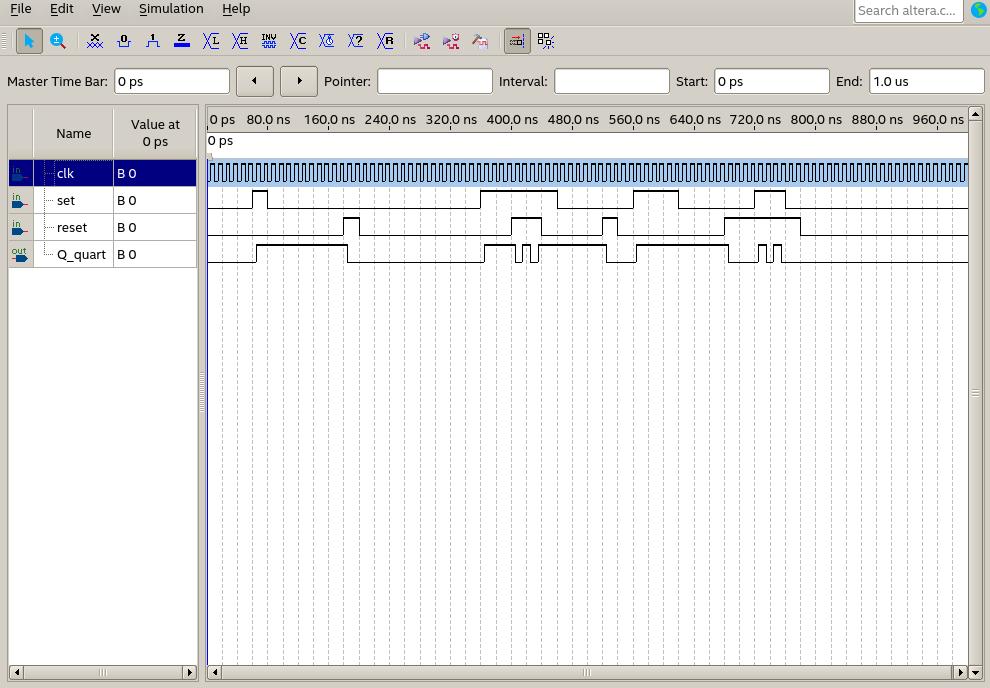

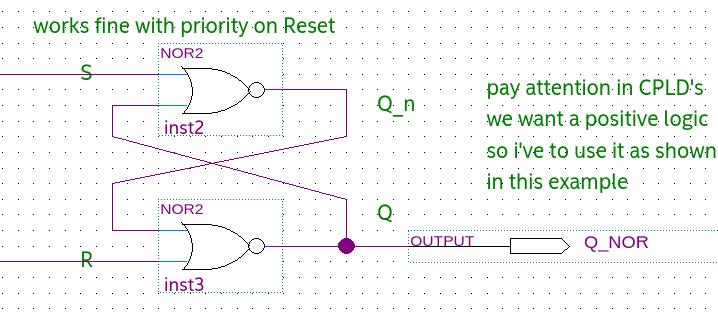

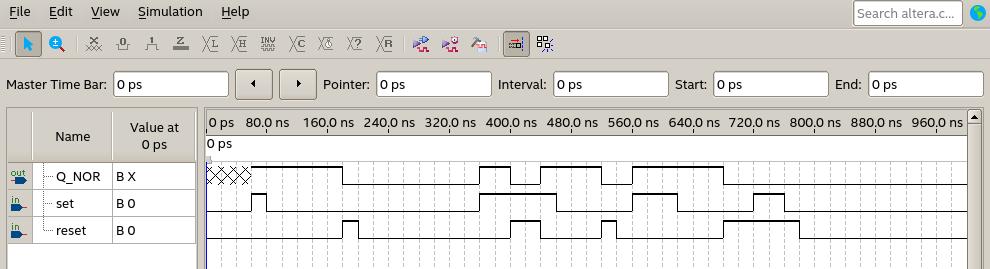

Die dritte Version mit zwei NOR Gatter

ModelSim

Schaut gut aus und funktioniert

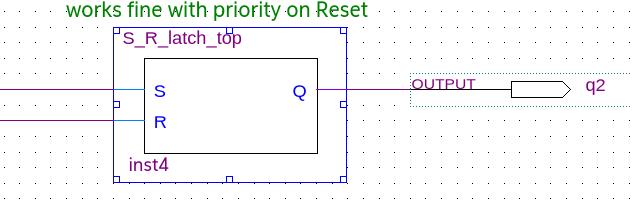

Die vierte Version

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity S_R_latch_top is

Port ( S : in STD_LOGIC;

R : in STD_LOGIC;

Q : out STD_LOGIC);

end S_R_latch_top;architecture Behavioral of S_R_latch_top is

signal Q2 : STD_LOGIC;

signal notQ : STD_LOGIC;

beginQ <= Q2;

Q2 <= R nor notQ;

notQ <= S nor Q2;

end Behavioral;

Schaut gut aus und funktioniert

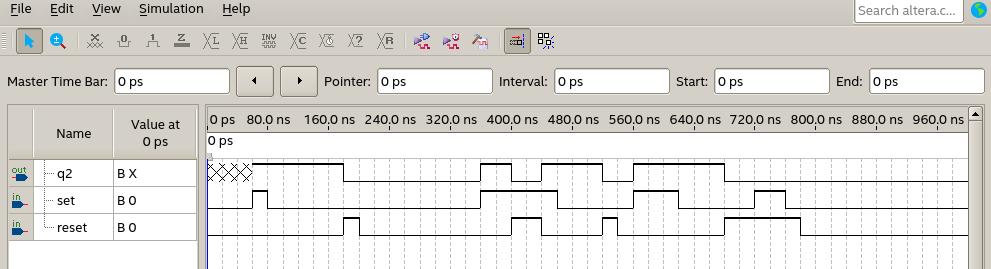

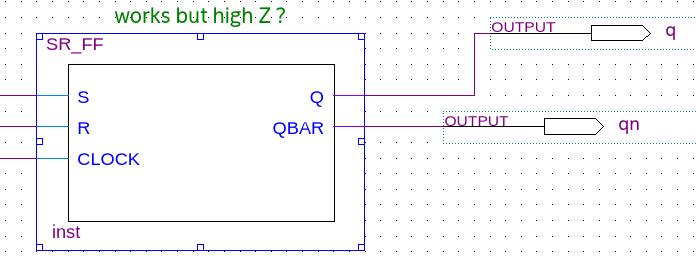

Noch eine andere Variante mit Takt

library ieee;

use ieee. std_logic_1164.all;

use ieee. std_logic_arith.all;

use ieee. std_logic_unsigned.all;entity SR_FF is

PORT( S,R,CLOCK: in std_logic;

Q, QBAR: out std_logic);

end SR_FF;Architecture behavioral of SR_FF is

begin

PROCESS(CLOCK)

variable tmp: std_logic;

begin

if(CLOCK='1' and CLOCK'EVENT) then

if(S='0' and R='0')then

tmp:=tmp;

elsif(S='1' and R='1')then

tmp:='Z';

elsif(S='0' and R='1')then

tmp:='0';

else

tmp:='1';

end if;

end if;

Q <= tmp;

QBAR <= not tmp;

end PROCESS;

end behavioral;

Wie man sieht Toggelt diese Variante nicht. macht aber im Hinteren Fall der Simulation doch etwas komisches, insofern dass hier Reset und Set auf High sind q2 bleibt LOW aber Qn geht auf LOW

Wie jeder sehen kann, selbst ein so einfaches Element wie ein RSFF hat seine Tücken.

- Anmelden, um Kommentare verfassen zu können